高端封装技术:攻克存储器系统性能和容量限制

高端封装技术:攻克存储器系统性能和容量限制

来源:SK海力士

在半导体行业竞争日趋激烈的背景下,封装工艺作为一种部署更小型、更轻薄、更高效、和更低功耗半导体的方法,其重要性日益凸显。同时,封装工艺也可响应半导体小型化技术的限制和满足其他市场需求。

封装工艺是指对半导体制成品进行包装的过程,使其免受损坏,同时将半导体电路中的电线与外部连接。此前,封装工艺通常被视为一种简单的辅助工作,属于半导体制造的后工序,而非确定半导体质量的前工序。然而,近年来,随着晶体管的特征尺寸缩小到5nm以下,加之半导体制造业在未来几年面临物理尺寸限制的可能性越来越大,封装技术也得到了前所未有的关注。

封装工艺关乎半导体产品,是与客户休戚相关的关键工艺,SK海力士肩负责任,承载使命,致力于实现最佳性能和最高品质。

下面我们将详细探讨封装技术,了解封装技术的未来趋势。

#01 对封装技术的重新思考

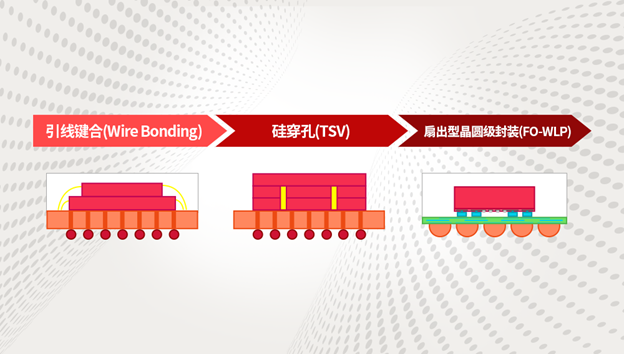

【图1】封装技术的发展历程

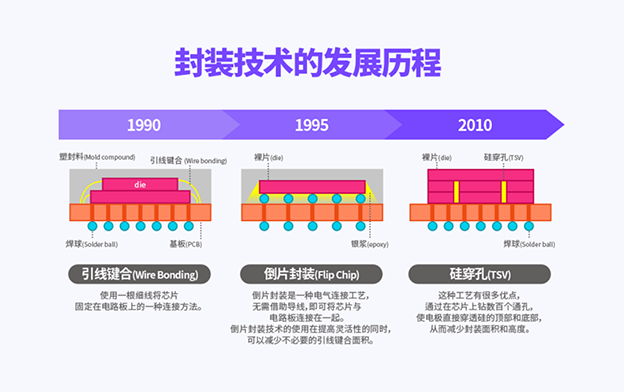

【图2】FO-WLP封装计划包含模压优先选项(die-first)和重新分配层(RDL)优先封装选项(来源:Micromachines,《EE Times》杂志)

随着市场对高性能和高容量存储器产品的需求不断增加,从十年前开始,诸如重新分配层(RDL)1、倒片封装(Flip Chip)2和硅穿孔(TSV)3等封装技术得到了积极广泛的应用【图1】。这些技术颠覆了传统的芯片级封装方法,在硅晶圆或芯片堆叠结构晶圆中进行工艺处理,大幅提高了产品的性能和容量。需要指出的是,SK海力士凭借业界领先的TSV堆叠技术引领市场发展,这其中包括高带宽存储器(HBM)封装存储器解决方案,以及用于服务器的高密度存储器(HDM)三维堆叠(3DS)技术【图2】。2016年,SK海力士率先应用批量回流焊(mass reflow)工艺?,将4块50 um厚芯片相互堆叠,并结合TSV堆叠技术,成功开发出一款服务器专用3DS存储器。近期,公司将这项技术应用于HBM产品的8层堆叠上。通过采用多个热假凸块作为散热路径,并使用具有优良导热性的塑封料作为间隙填充材料,SK海力士大大改善了因存储器带宽增加而引起的散热问题,同时也大幅降低了TSV的高昂制造成本。

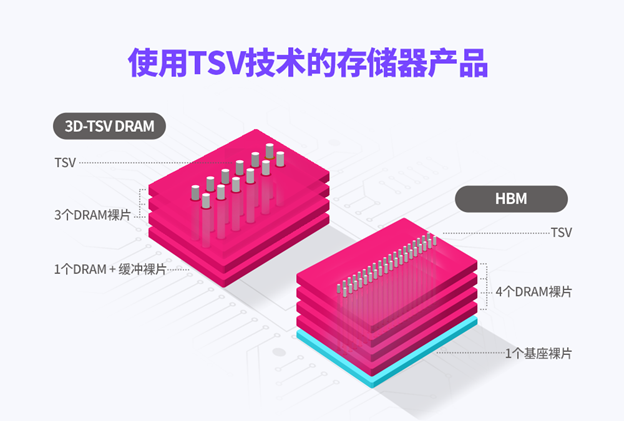

【图3】使用TSV技术的存储器产品

#02 存储器容量需求影响芯片技术

HBM中所使用的TSV技术是一种使用硅穿孔电极(TSV)和微凸块垂直堆叠多个芯片(通常为4-8个芯片)的方法。由于市场对高容量存储器产品需求不断增加,预计未来将需要12-16层甚至更高的多芯片堆叠技术。为了实现这一目标,不仅需要减小芯片的厚度和凸块电极的尺寸,而且在不久的将来还需要应用混合键合(hybrid bonding)技术?,去除芯片之间的填充物,使其直接连接到铜电极上【图3】。

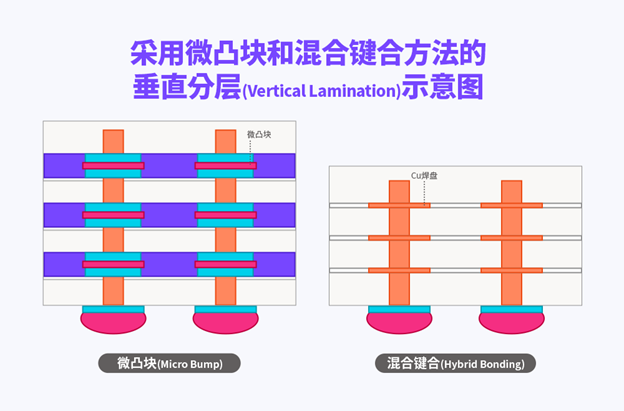

【图4】采用微凸块和混合键合方法的垂直分层(Vertical Lamination)示意图

与使用微凸块的方法相比,混合键合方法可以大幅缩小电极尺寸,从而增加单位面积上的I/O数量,进而大幅降低功耗。与此同时,混合键合方法可以显著缩小芯片之间的间隙,由此实现大容量封装。此外,它还可以改善芯片散热性能,有效地解决因耗电量增加而引起的散热问题。

#03 平衡容量与热量生成

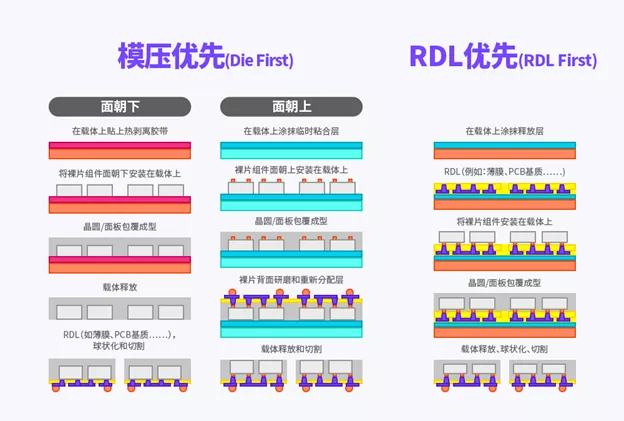

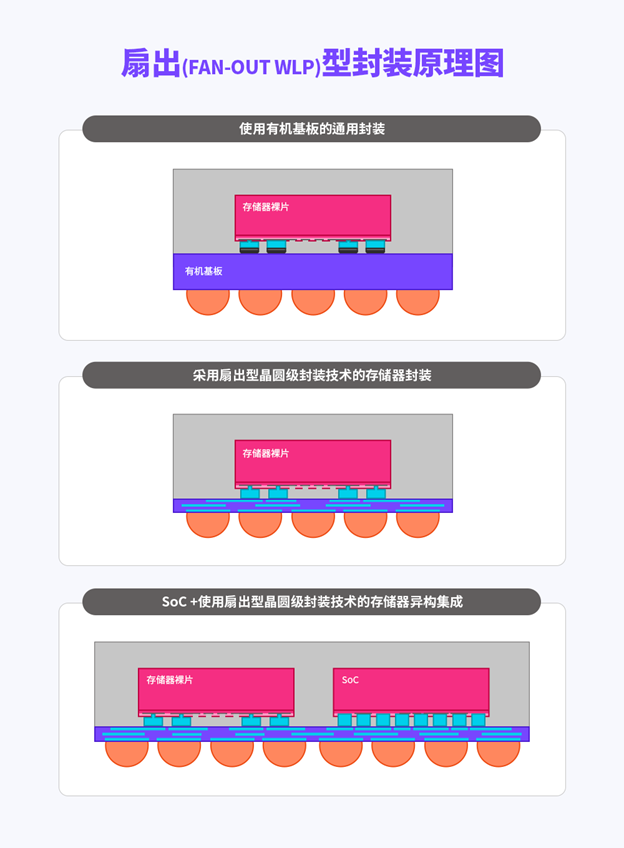

除了需要TSV技术在容量方面的创新外,人们还需要高速芯片和存储器芯片的异构集成解决方案?,以最大限度地发挥系统内存储器产品的特性。此外,人们还需要全新封装解决方案,来解决因存储器芯片功率增加而引起的散热问题,以及因堆叠的存储器芯片数量增加而产生的厚度限制要求。扇出型晶圆级封装(Fan-out WLP)?是一种通过使用晶圆级重新布线技术将芯片的I/O焊盘迁移到芯片外部区域的技术。这种先进的封装技术目前被积极应用于应用处理器(AP)和电源管理芯片(PMIC)等非存储器芯片上。该技术可以使用重新分配层来替代基板,从而减小封装厚度。此举还可以改善芯片散热效果,因此人们正在积极研究将这一技术应用于存储器产品的可行性。

【图5】扇出(fan-out WLP)型晶圆级封装示意图

此外,为了解决存储器装置的技术缩减限制和功率消耗问题,目前人们正在积极研究异构芯片(而非存储器芯片)集成技术。通过采用扇出型封装技术可以在不同形式的封装中实现上述目标,不仅提高了存储器产品的性能,而且可以通过新的应用场景实现扩展【图4】。扇出型封装技术可以与包括引线键合、 TSV、重新分配和凸块技术等在内的各种封装技术相融合,对各种形式的存储器产品进行封装。由于存储器芯片需要足够的容量,扇出型晶圆级封装结构将成为一项关键实施技术,能够实现垂直堆叠。除了通用的扇出型RDL技术外,存储器产品的扇出型晶圆级封装还必须从多个堆叠芯片的I/O垂直连接扇出RDL布线,因此,确保电气特性和布线质量至关重要。

#04 封装转型,促进增长

研究发现,使用TSV技术和扇出型技术的3D堆叠技术预计将分别以每年20%和15%的速度增长。这也表明,这些都是高端封装领域的代表性技术。TSV和扇出型晶圆级封装技术正在不断发展完善,以便更好地消除当前存储器产品面临的各种局限性。过去,封装技术为存储器产品创造了大量的附加价值。因此,SK海力士将继续推进高端封装技术的转化与专业化升级,在满足存储器产品需求的同时,促进创新,并积极响应市场需求。

参考来源

[1] 重新分配层(Ridistribution Layer,简称RDL):一种重新布线技术;RDL技术旨在重新排列已经在晶圆上形成的焊盘,通过形成额外的金属布线层,将焊盘重塑到所需位置。

[2]倒片封装(Flip Chip):在芯片的焊盘上形成凸点(几十微米(?)大小,称为焊球),将凸点翻转然后与基板键合的方法

[3]硅穿孔(Through-siliconvia, 简称TSV):一种通过在硅芯片内部钻孔(通孔)形成通过电极,然后将多个芯片垂直3D堆叠的方法;与引线连接方法相比,该方法封装面积更小,并且在相同厚度下可以堆叠更多的芯片。此外,由于该方法可以在最短的距离内连接多个I/O,因此可以达到实现高带宽和降低功耗两全其美的效果。(请点击此处参阅相关文章。)

[4]批量回流模制底部填充(Mass reflow molded underfill,简称MR-MUF):将多个芯片放置在下层基板上,通过回流焊一次性粘合,然后同时用模塑料填充芯片之间或芯片与基板之间间隙的方法,该方法主要用于倒片封装和TSV芯片堆叠方法。

[5]混合键合:一种同时键合金属电极(如铜电极)和无机绝缘层的方法;该方法可以将至少两个不同的芯片集成到同一个封装中,缩小互连间距,有望广泛应用于芯片(SoC)裸片、SoC存储器和存储器上的多系统垂直堆叠。

[6]异构集成解决方案(Heterogeneous Integration Solution):一种在同一封装中部署不同类型(异构)器件的方法

[7]扇出型晶圆级封装(Fan-out wafer-level packaging, 简称Fan-out WLP):通过扩展芯片,在外部区域形成一个用于外部连接的球状端子。这种方法无需使用PCB基板,可以减小封装厚度,节约PCB基板成本。此外,这种方法还可以通过重新分配,简化在水平方向上桥接异构芯片的操作,因而可以用于多功能和高性能的存储器系统中。

(声明:本文版权归原作者所有,转发仅为更大范围传播,若有异议请联系我们修改或删除:wang@cgbtek.com)