碳化硅产业链(上游)

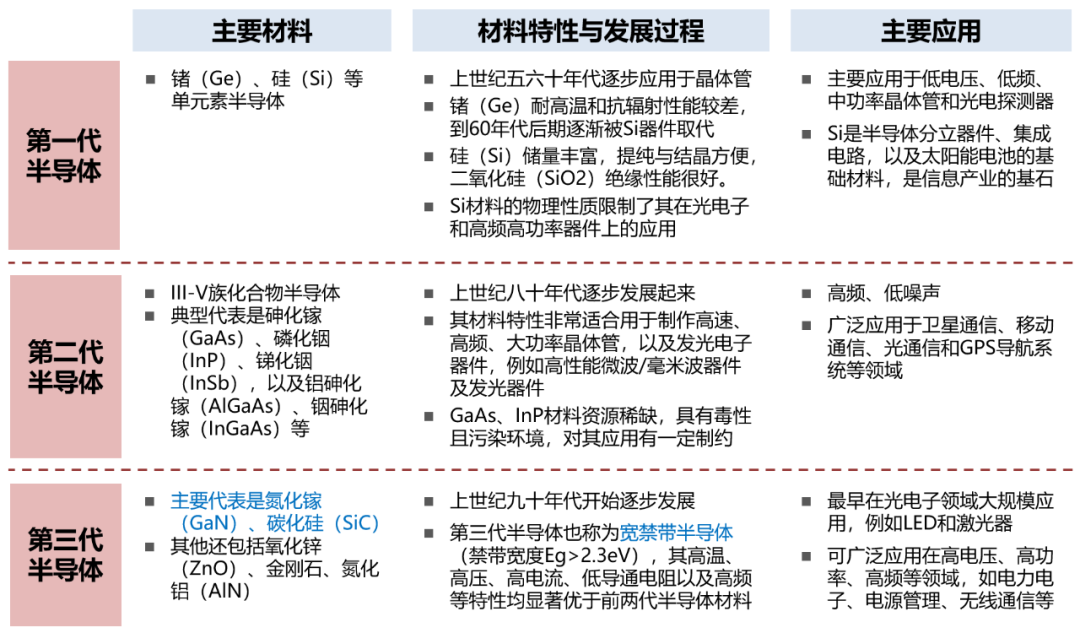

碳化硅介绍

耐高温。碳化硅的禁带宽度是硅的2-3倍,在高温下电子不易发生跃迁,可耐受更高的工作温度,且碳化硅的热导率是硅的4-5倍,使得器件散热更容易,极限工作温度更高。耐高温特性可以显著提升功率密度,同时降低对散热系统的要求,使终端更加轻量和小型化。 耐高压。碳化硅的击穿电场强度是硅的10倍,能够耐受更高的电压,更适用于高电压器件。 耐高频。碳化硅具有2倍于硅的饱和电子漂移速率,导致其器件在关断过程中不存在电流拖尾现象,能有效提高器件的开关频率,实现器件小型化。 低能量损耗。碳化硅相较于硅材料具有极低的导通电阻,导通损耗低;同时,碳化硅的高禁带宽度大幅减少泄漏电流,功率损耗降低;此外,碳化硅器件在关断过程中不存在电流拖尾现象,开关损耗低。

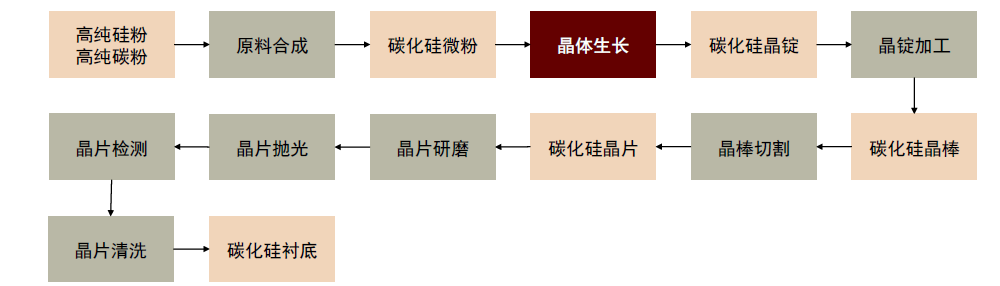

以高纯碳粉、高纯硅粉为原料合成碳化硅粉,在特殊温场下生长不同尺寸的碳化硅晶锭,再经过多道加工工序产出碳化硅衬底。核心工艺流程包括:

原料合成:将高纯的硅粉+碳粉按配方混合,在2000°C以上的高温条件下于反应腔室内进行反应,合成特定晶型和颗粒度的碳化硅颗粒。再通过破碎、筛分、清洗等工序,得到满足要求的高纯碳化硅粉原料。 晶体生长:为碳化硅衬底制造最核心工艺环节,决定了碳化硅衬底的电学性质。目前晶体生长的主要方法有物理气相传输法(PVT)、高温化学气相沉积法(HT-CVD)和液相外延(LPE)三种方法。其中PVT法是现阶段商业化生长SiC衬底的主流方法,技术成熟度最高、工程化应用最广。

SiC 衬底制备难度大,导致其价格居高不下

温场控制困难:Si 晶棒生长只需 1500℃,而 SiC 晶棒需要在 2000℃以上高温下进行生长,并且 SiC 同质异构体有 250 多种,但用于制作功率器件的主要是 4H-SiC 单晶结构,如果不做精确控制,将会得到其他晶体结构。此外,坩埚内的温度梯度决定了 SiC 升华传输的速率、以及气态原子在晶体界面上排列生长方式,进而影响晶体生长速度和结晶质量,因此需要形成系统性的温场控制技术。与 Si 材料相比,SiC 生产的差别还在如高温离子注入、高温氧化、高温激活等高温工艺上,以及这些高温工艺所需求的硬掩模工艺等。 晶体生长缓慢:Si 晶棒生长速度可达 30~150mm/h,生产 1-3m 的硅晶棒仅需约 1 天的时间;而 SiC 晶棒以 PVT 法为例,生长速度约为 0.2-0.4mm/h,7 天才能生长不到 3-6cm,长晶速度不到硅材料的百分之一,产能极为受限。 良品参数要求高、良率低:SiC 衬底的核心参数包括微管密度、位错密度、电阻率、翘曲度、表面粗糙度等,在密闭高温腔体内进行原子有序排列并完成晶体生长,同时控制参数指标,是复杂的系统工程。 材料硬度大、脆性高,切割耗时长、磨损高:SiC 莫氏硬度达 9.25 仅次于金刚石,这导致其切割、研磨、抛光的加工难度显著增加,将一个 3cm 厚的晶锭切割 35-40 片大致需要花费 120 小时。另外,由于 SiC 脆性高,晶片加工磨损也会更多,产出比只有 60%左右。

发展趋势:尺寸增加+价格下降

全球SiC市场6英寸量产线正走向成熟,领先公司已进军8英寸市场。国内正在开发项目以6英寸为主。目前虽然国内大部分公司还是以4寸产线为主,但是产业逐步向6英寸扩展,随着6英寸配套设备技术成熟后,国产SiC衬底技术也在逐步提升大尺寸产线的规模经济将会体现,目前国内6英寸的量产时间差距缩小至7年。更大的晶圆尺寸可以带来单片芯片数量的提升、提高产出率,以及降低边缘芯片的比例,研发和良率损失部分成本也将保持在7%左右,从而提升晶圆利用率。

衬底直径及大直径衬底占比将不断增加,助力全产业链降本。预计未来30年,大尺寸衬底的比例将不断增加,在大部分衬底提供商具备新型大尺寸量产能力,一轮尺寸更新周期迭代完成后,衬底单位面积价格会迎来相对快速的降低。

SiC衬底价格会随着尺寸增加有所下降,同时进一步带来销量的稳步上升。目前衬底发展最重要的方向趋势是扩大直径,这会降低衬底生产成本进而降低售价,价格的下降也会加速SiC衬底在各领域内的渗透。根据CASA数据预测,SiC衬底和外延随着产业技术逐步成熟(良率提升)和产能扩张(供给提升),预计衬底价格将以每年8%的速度下降。

碳化硅晶体生长的过程中会不可避免地产生缺陷、引入杂质,导致衬底材料的质量和性能都不够好。而外延层的生长可以消除衬底中的某些缺陷,使晶格排列整齐。控制碳化硅外延缺陷是制备高性能器件的关键,缺陷会对碳化硅功率器件的性能和可靠性有严重影响。TSD和TED基本不影响最终的碳化硅器件的性能,而BPD会引发器件性能的退化。堆垛层错、胡萝卜缺陷、三角形缺陷、掉落物等缺陷,一旦出现在器件上,器件就会测试失败,导致良率降低。

碳化硅外延的制作方法包括:化学气相淀积(CVD)、分子束外延(MBE)、液相外延法(LPE)、脉冲激光淀积和升华法(PLD)等,其中CVD法是最为普及的4H-SiC外延方法,其优势在于可以有效控制生长过程中气体源流量、反应室温度及压力,精准控制外延层的厚度、掺杂浓度以及掺杂类型,工艺可控性强。早期碳化硅是在无偏角衬底上外延生长的,受多型体混合影响,外延效果不理想。随后发展出台阶控制外延法,在不同偏角下斜切碳化硅衬底,形成高密度外延台阶,在实现低温生长的同时稳定晶型的控制。随后引入TCS,突破台阶控制外延法的限制,将生长速率大幅提升至传统方法的10倍以上。目前常用SiH4、CH4、C2H4作为反应前驱气体,N2和TMA作为杂质源,使用4°斜切的4H-SiC衬底在1500-1650℃下生长外延。

转载微信公众号:半导体信息

声明:本文版权归原作者所有,转发仅为更大范围传播学习,若有异议请联系我们修改或删除:market@cgbtek.com

联系方式:

服务热线/Service: 400-650-7658 + 8613910297918

邮箱/Email :sales@cgbtek.com

公司网站/Website: http://www.cgbtek.com

生产基地/Address: 河北省廊坊市香河机器人产业园3期A栋